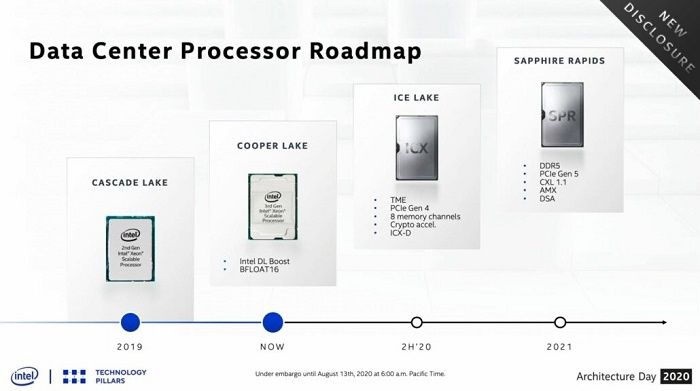

Intel is paving the way for a major revival in the server and data center market with its new Xeon Scalable Ice Lake SP chips, part of its Whitley business platform.

Intel Xeon Scalable Ice Lake-SP, new filtered details

The company is confident that these chips will be able to compete much more effectively with AMD EPYC’s offering, which is about to launch its new Milan chips later this year.

Here is the first overview of Intel’s upcoming “Whitley” business platform, consisting of the “Ice Lake-SP” processors, published on Twitter by the famous user and filter momomo_us.

The platform will introduce a new socket LGA4189, necessitated by Intel to increase the memory channels per socket to 8, compared to the 6 of the current “Cascade Lake-SP” generation.

Intel will also do an important step forward by adding support for PCI-Express 4.0, with each socket connecting up to 64 PCI-Express 4.0 lanes to the CPU. These are typically connected to the CPU as three x16 slots, two x8 slots, one x4 chipset bus, and a 10 GbE controller.

Ice Lake SP chips support up to 8 memory channels, which work with memory up to DDR4-3200 with ECC. The other key component will be the C621A PCH chipset. This new chipset communicates with the “Ice Lake-SP” processor via a PCI Express 3.0 x4 connection.

Finally, it is shown that the top-of-the-line Ice Lake SP chip is manufactured with a 10nm node and could have a TDP of up to 270 W.