Some details about the future AMD EPYC Milan processors have become known, the new generation of AMD EPYC Milan processors, which are expected to hit the servers and data centers by the end of this year.

AMD EPYC Milan will increase its performance by 10-20% over Rome

We know from last year that AMD EPYC Milan is designed under the TSMC 7nm node and will offer up to 64 cores, all under the new Zen 3 architecture, and will also support DDR4 and PCI-Express 4.0.

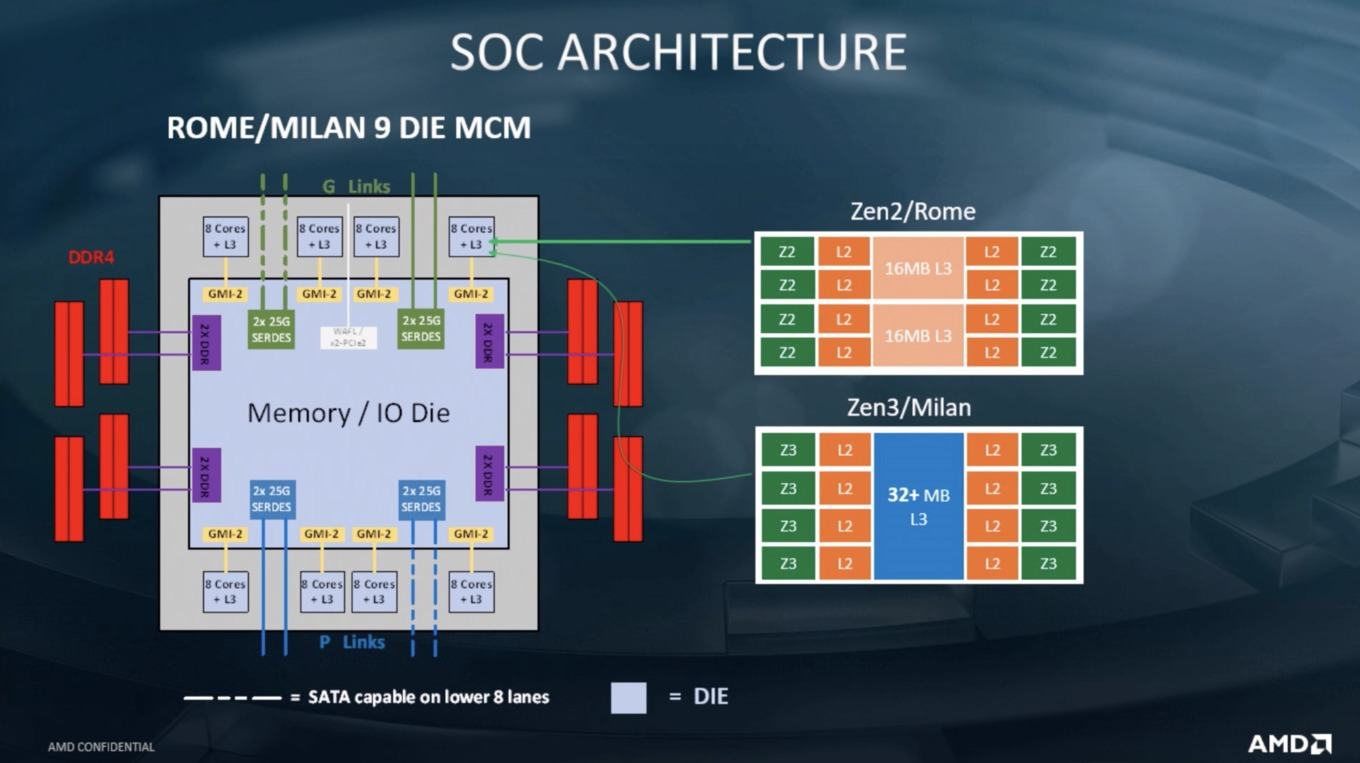

There are also changes in the design of the Core Compute Die (CCD) and therefore the Core Compute Complex (CCX). The current CCDs consist of two CCX clusters each, in which the L3 cache is also divided into two 16 MB blocks. For Zen 3 this looks different now. A schematic diagram shows the CCD with a common L3 cache.

As you can see on the slides, the L3 cache will be 32 MB for Zen 3. The number of cores is identical to eight per CCD, but the CCX clusters in their previous form no longer exist.

For the EPYC processors with up to 32 cores, AMD expects a +20% increase in performance compared to the Rom processors with Zen 2. For the larger EPYC processors with up to 64 cores, AMD expects a performance increase of about 10 to 15%.

Apparently AMD can achieve higher clock speeds on processors with fewer cores, so the performance increase is correspondingly greater with fewer cores. This is AMD’s main goal with the new EPYCs, and it is normal to expect the same with Zen 3, which is to improve CPI, clock speeds, and performance with a single core.